- #4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE DRIVER#

- #4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE VERIFICATION#

- #4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE CODE#

Okay so without further delay, here’s the code for decoder. In Verilog HDL, memories can be defined as a two dimensional array using reg data type, as illustrated below: reg 3:0 MYROM 15:0. Also, this type of enabling is called active low, since the chip gets activated when the enable turns low(i.e. Thus, this enable can be used as a switch by many devices in order to keep this device “on” only in the time of need. You can see that the design modifies in a sense that if the enable is logic 0 => the output becomes zero no matter the input. Truth Table for 3 to 8 decoder with enable Take a look at the transformed truth table Enable

#4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE DRIVER#

Yes, the theoretical part of the design is almost over with the understanding of the enable input, which is the driver of the combinational logic.

Also using this table to simplify the logic of the design we initially thought off. This is the beauty of digital Electronics. Truth TableĪny digital circuit can be realized using Truth Table. Since, we now understand the concept behind the decoder, we should start with the logic oriented part. In Verilog Coding, of a particular combinational circuit it is necessary to know the number of input/output a particular chip may require. Thus, if we have 3-bit input we will have 2 3 = 8-bit output. So, if there are N inputs, the decoder will produce a maximum of 2 n outputs.

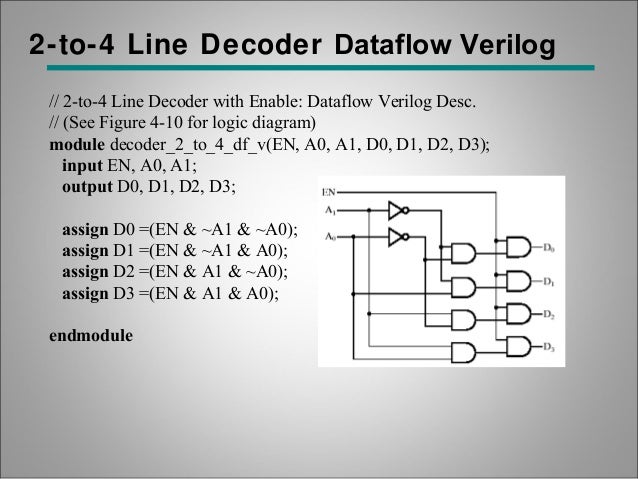

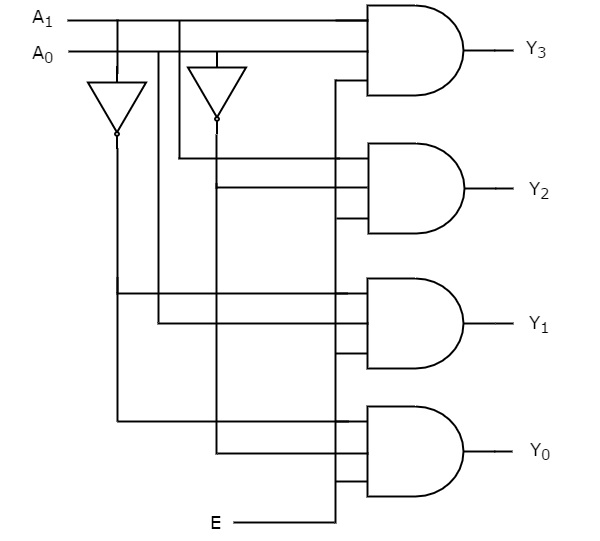

For example, the above is 1-of-n type of binary decoder, meaning that when, an input is given only 1 or none of the output is activated.Ī binary decoder is usually implemented as a standalone IC or as a part of more complex ICs. There are few different types of decoders. At any time, only one of these 4 inputs can be ‘1’ in order to get the respective binary code at the output.įigure 5.3 to 8 Decoder using Verilog Programming Content to be covered :Ī decoder is a digital circuit, that helps convert an given n coded input to a 2 n outputs.Ī decoder various applications such as data multiplexing and data demultiplexing, seven segment displays, and as address decoders for memory and port-mapped I/O. The 4 to 2 Encoder consists of four inputs Y3, Y2, Y1 & Y0 and two outputs A1 & A0. Therefore, the encoder encodes 2 n input lines with ‘n’ bits. It will produce a binary code equivalent to the input, which is active High. 2) EncoderĪn Encoder is a combinational circuit that performs the reverse operation of Decoder.It has maximum of 2 n input lines and ‘n’ output lines, hence it encodes the information from 2 n inputs into an n-bit code. Hence the output of the decoder is dependent on whether the Enable is high or low. When Enable is 1, the AND gates get one of the inputs as 1, and now the output depends upon the remaining inputs. If Enable is 0, all AND gates are supplied with one of the inputs as 0 and hence no output is produced. Only a small change in the implementation is required: the Enable input is fed into the AND gates which produce the outputs. Output is only generated when the Enable input has value 1 otherwise, all outputs are 0. This extra input allows the decoders outputs to be turned “ON” or “OFF” as required. Therefore, whichever output line is “HIGH” identifies the binary code present at the input, in other words it “decodes” the binary input.Some binary decoders have an additional input pin labelled “Enable” that controls the outputs from the device. The binary inputs A and B determine which output line from Q0 to Q3 is “HIGH” at logic level “1” while the remaining outputs are held “LOW” at logic “0” so only one output can be active (HIGH) at any one time. Logic Diagram and Truth table of 2-to-4 Decoder Each output represents one of the minterms of the 2 input variables, (each output = a minterm).įigure 3. a) Write Verilog HDL behavioral style code for 2-to-4 decoder. The 2 binary inputs labelled A and B are decoded into one of 4 outputs, hence the description of 2-to-4 binary decoder. The outputs are represented by the 16-bit vector Y y0 y1. The 2-to-4 line binary decoder depicted above consists of an array of four AND gates. The name “Decoder” means to translate or decode coded information from one format into another, so a digital decoder transforms a set of digital input signals into an equivalent decimal code at its outputĪ decoder is a combinational circuit that converts binary information from n input lines to a maximum of m=2^n unique output lines.įigure 2. Encoders convert 2 N lines of input into a code of N bits and Decoders decode the N bits into 2 N lines. This is what encoders and decoders are used for. Introductionīinary code of N digits can be used to store 2 N distinct elements of coded information.

#4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE VERIFICATION#

Implementation and verification of decoder/de-multiplexer and encoder using logic gates.

0 kommentar(er)

0 kommentar(er)